大數據時代對存儲器的性能提出了極高的要求,尤其是類腦計算、邊緣計算急需功耗極低的存儲器。在新型存儲器中,相變存儲器(PCM)是與CMOS工藝最兼容,技術最成熟的存儲技術。2015年,Intel和Micron推出了傲騰三維相變存儲芯片,速度和壽命比固态閃存硬盤要快一千倍,其三維堆疊技術也使容量高出了十倍。然而,由于在相變過程中需要将存儲介質熔化冷卻,導緻相變存儲器的功耗極高且發熱嚴重,限制了存儲容量的進一步提高,也大大增加了其制造成本。因此,降低相變存儲器的功耗将便于進一步提升存儲器數據密度,提高其在半導體存儲市場核心競争力,此外降低功耗可以改善存儲器散熱問題,減少相鄰單元間的熱串擾,從而提高器件穩定性和整體性能。目前最先進的幾十納米制程的單個相變存儲單元擦寫功耗達到了40pJ左右,而實驗室制備的百納米大小的器件功耗達到1000pJ以上。

為了解決相變存儲器中高功耗的瓶頸問題,6774澳门永利信息存儲材料及器件研究所(ISMD)聯合西安交通大學材料創新設計中心(CAID)研發了一種網狀非晶結構的相變存儲器,功耗達到了0.05pJ以下,比主流産品功耗低了一千倍。與普通“蘑菇結構”的相變存儲器不同,這種新型存儲器利用相變材料的自發分相在介質中形成了一些“導電島”,而對該存儲器的擦寫隻需要将這些島鍊接或者斷開即可。除了低功耗以外,該相變存儲器擁有一緻性好且壽命長的優點。這種結構的相變存儲器在制備工藝上同樣具有很大優勢,到目前為止,所有降低功耗的方法都遵循功耗和數據存儲設備大小之間的直接縮放,這提高了器件制備的工藝難度,而對于網狀非晶結構的相變存儲器提出了一種可以打破功耗與器件大小的比例依賴關系的材料設計策略,該合金可以通過濺射沉積合成,無需添加複雜的制造工藝,這為PCM單元的高密度集成提供了另一種方法。該材料設計策略使得能在一個正常尺寸的器件(250nm孔徑)中産生幾十個fJ的超低的擦寫能耗。

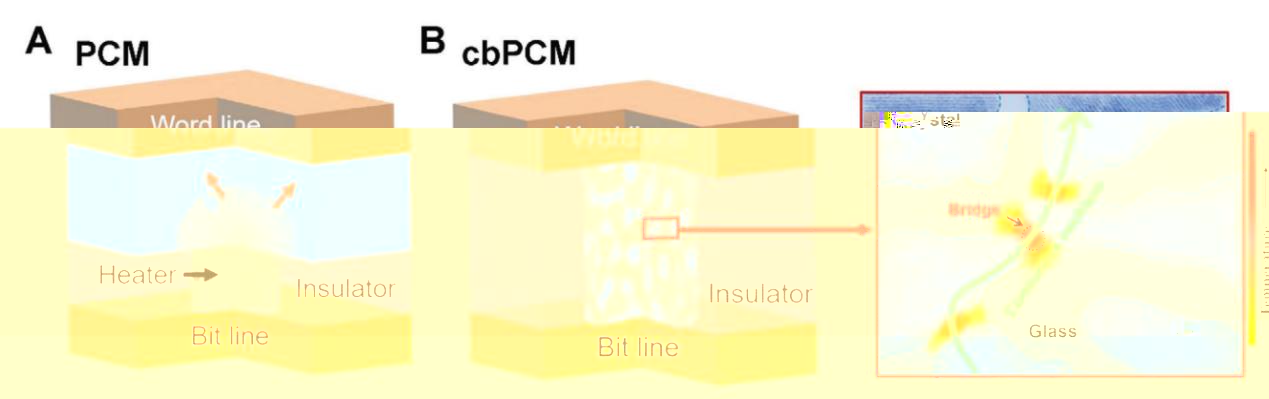

該導電橋相變存儲器(Conductive-Bridge Phase-Change Memory,cbPCM)的原理是在PCM合金内部産生一個幾納米粗細的導電通道,從而使開關體積最小化且電流路徑可以很容易地打開和關閉。如下圖B中所示,導電通道由低電阻和低Tc(相變溫度)的PCM區域組成,即連接在一起的晶體納米區域(CNDs),它們被高電阻态的非晶态區域包圍。這些CNDs幾乎相互連接,隻有微小的非晶間隙隔開。循環開關過程中的相變僅在CNDs之間的微小間隙中進行。換句話說,電流路徑的電阻是由連接CND的小橋段控制的,通過将缺失的鍊路(紅色區域)轉換為導電橋,電流和由此産生的焦耳熱很可能被集中起來,在許多CNDs上形成一條導電鍊。該方案利用了焦耳加熱引起的界面相變,這在納米制造模式(和摻雜)GST存儲單元中被證明是可能的(将擦寫電流降低到20μA)。

如前文所述,cbPCM的擦寫能耗可以達到達到極低的幾十個fJ,對于典型的PCM設備每次擦寫操作需要幾十個pJ到幾十個nJ,cbPCM的能耗降低到了典型PCM的千分之一級别。在此工作之前,全世界功耗最低的相變存儲器是由碳納米線實現的,其擦寫能耗約為100fJ,通過使用自對準的GST納米線和CNT電極,能耗可以進一步降低到約80fJ,然而這種碳納米線工藝要實現大規模半導體制造還需要很長的時間。下圖中展示了典型PCM設備中擦寫能量值與電極接觸面積的關系(虛線所示),可以看到我們的基于GSO的設備具有超低編程能耗,在正常尺寸下功耗遠低于典型PCM設備,打破了之前所有設備建立的功耗與電極接觸面積的比例關系。因此,cbPCM的功耗和制備難度方面相比于典型PCM和碳納米線器件都具有很大的優勢。

本工作利用精心設計的GSO合金成功設計和制造了納米級導電橋PCM器件,打破了能量大小的直接尺度相關性,達到了相變存儲單元的低編程能量。該合金與目前的半導體生産線兼容,并可以實現一次性濺射,确保簡單和低成本的生産。此外,該相變材料也在未來表現出更多的用途,例如基于GSO的單元也可以呈現多級電阻能力,可以通過更強的重置脈沖來增加或斷開更多的連接橋,或使用更長的SET脈沖來結晶更大比例的非均勻網絡,這種編程模式帶來的波動和可變性可以應用在對随機相變神經突觸的模拟,在生物神經網絡中的信号編碼和傳輸中起着關鍵作用。随着GSO單元接近生物神經電脈沖的功耗,該cbPCM器件的性能将優于傳統的基于GST的PCM器件。

該成果以“Designing Conductive-Bridge Phase-Change Memory to Enable Ultralow Programming Power”為題發表在《AdvancedScience》上。論文的第一作者為楊哲博士、王疆靖博士、李博文。通訊作者為徐明教授、缪向水教授、張偉教授和馬恩教授。該研究是在國家自然科學基金、國家重點研發計劃和國家02專項的資助下開展的,材料的實驗表征受到了中科院上海微系統所朱敏研究員的傾力相助。

文章信息:

Yang, Z., Li, B., Wang, J.-J., Wang, X.-D., Xu, M., Tong, H., Cheng, X., Lu, L., Jia, C., Xu, M., Miao, X., Zhang, W., Ma, E., Designing Conductive-Bridge Phase-Change Memory to Enable Ultralow Programming Power. Adv. Sci. 2022, 2103478.DOI:10.1002/advs.202103478

https://onlinelibrary.wiley.com/doi/10.1002/advs.202103478